高清晰多媒体接口TMDS通道编码方法及实现

高清晰多媒体接口TMDS通道编码方法及实现

阳昕1,熊江1,黄艺珍2,易清明2

(1.炬芯(珠海)科技有限公司,广东 珠海 519085;2.暨南大学信息科学技术学院,广东 广州 510632)

摘 要 本文研究HDMI所采用最小差分变换编码技术对数字信号无压缩的高速传输方法,并对HDMI三大工作周期所用到的编码方法进行说明。最后根据编码方法使用Verilog语言进行实现并在Xilinx ISE9.1平台上进行功能仿真及分析,仿真结果表明TMDS编码技术能够实现数据的高效传输,确保传输数据流达到直流平衡,提高了系统的抗干扰能力。

关键词:高清晰度多媒体接口;最小变换差分信号;直流平衡

中图分类号:TP37

TMDS Channel Coding Method and Implementation of HDMI

Yang Xin1,Xiong Jiang1,Huang Yizhen2, YI Qingming2

(1. Actions (Zhuhai) Technology Co., Limited, Zhuhai 519085,Guangdong,China;

2. School of Information Science and Technology, Jinan University, Guangzhou 510632,Guangdong,China)

Abstract This paper proposes the high-speed transmission method of uncompressed digital signals using TMDS, and describes the encoding methods which are used by HDMI. Then VerilogHDL was used to realize the TMDS algorithm, and simulate successfully with the Xilinx ISE9.1 simulation tool. The result showed that the data can be transmitted efficiently, the algorithm can ensure that the transmission of data streams achieves DC balance and improves anti-jamming capability of the system.

Key words HDMI; TMDS;DC balance

HDMI(High-Definition Multimedia Interface)称为高清晰度多媒体接口,是首个支持在单线缆上传输不经过压缩的全数字高清晰度、多声道音频和智能格式与控制命令数据的数字接口。由于HDMI接口应用方便,能适应未来高清音视频对带宽的要求,目前HDMI接口在消费类电子中已成为行业标准。

HDMI使用了DVI中的最小变换差分信号 ( Transition-minimized differential signaling,TMDS),它不但提高传输的稳定性,还延长了导线的传输距离[1],能大大提高数据传输的抗干扰性。

本文根据HDMI三大工作周期(控制周期、数据岛周期和视频周期)所用到的TMDS通道编码方法并进行研究分析。最后根据编码方法使用硬件描述语言Verilog HDL对TMDS通道编码方法进行编码实现,并使用Xilinx ISE9.1仿真工具对其进行行为级仿真和分析。

1 TMDS介绍

TMDS是Silicon Image公司开发,用于将图形数据送到显示器的技术。它通过异或、异或非等算法将8位数据转换成10位。这种算法使得被传输信号过渡过程的上冲和下冲减小,直流信号也接近平衡。它以差分形式发送信号,信号的优化使信号对传输线的电磁干扰减少,传送的数据也趋于直流平衡。这种先进的编码技术使数据在接收端得到可靠的恢复。因此通过TMDS传输,传输距离能得到显著提高。

HDMI输入的源编码格式包括视频像素数据、控制数据和数据包。其中数据包中包含有音频数据和辅助信息数据,同时HDMI为了获得声音数据和控制数据的高可靠性,数据包中还包括一个BCH错误纠正码。HDMI数据信息的处理可以有多种不同的方式,但最终都是在每一个TMDS通道中包含8位的视频数据、4位的数据包和2位的控制数据。因而HDMI的数据传输过程可以分成三个部分:视频数据传输期、岛屿数据传输期和控制数据传输期[3]。

2 TMDS编码方法

2.1 视频数据周期

TMDS视频数据编码涉及一个重要的控制信号VDE(Video Data Enable)。当VDE=1时传输视频数据;VDE=0时视频数据无效。

任意一个视频数据周期前面均存在一个导言preamble信号。在导言信号和视频数据周期之间还存在由两个像素视频组成固定的10比特字符信息的保护带leading GB,同时还可注意到在视频数据结束时是没有后向保护带的。视频开头防护带值编码如下[4]:

case(TMDS Channel Nunmber):

0: q_out[9:0]= 0’b1011001100;

1: q_out[9:0]= 0’b0100110011;

2: q_out[9:0]= 0’b1011001100;

Endcase

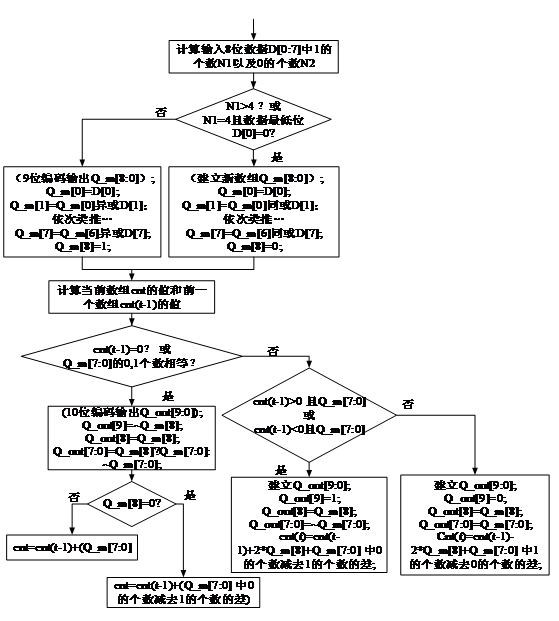

视频数据周期使用最小化差分传输编码方法将三通道的8比特视频数据编码成10位的直流平衡码。最小化传输编码方法定义的参数说明如表1所示,最小化传输编码方法流程图如图1所示。

表1 最小化传输编码方法定义的参数说明

|

q_m |

表示编码转换过程中的一个中间传递值 |

|

D |

用来对编码器输入数据进行设置 |

|

q_out |

10位数据编码输出值 |

|

Cnt |

跟踪并存储数据流高低电平差异的寄存器。 |

|

N1(x) |

编码变换过程中返回变量x中值为1的个数 |

|

N0(x) |

编码变换过程中返回变量x中值为0的个数 |

图1 最小化差分传输编码算法

最小化传输编码方法过程主要分为两个阶段:

第一阶段,将输入8比特数据采用最小化差分变换方法编码成9比特的编码数据。保持最低有效位不变,然后将其余的7位数据与其上一位最小变换码进行同或(XNOR)或者异或(NOR)运算来获得D[1]~D[7]的八位编码数据,XOR和XNOR逻辑之间的选择是以使得所编码的值中包含尽可能少的跳变为出发点,转换后的第9位信息位就用来表示变换方式标志位,其值为0时采用异或运算,否则采用同或运算。

第二阶段,将9比特数据变换成最终的10位编码数据,第10位属于直流平衡码标志位,它表示前面9位数据编码是否已经做了取反操作,1表示对前9位数据做了取反,0则没有取反。即它是编码器为了使数据编码后达到一种直流平衡效果而用来选择第一阶段编码中前面9位数据是否需要取反的一个标志位[2]。这个过程需要对编码数据中的0和1的个数进行计算,如果第一阶段编码后前9位数据1的个数比0的个数多,且将要传输的编码中1比0多时,则将前8位数据取反,并将第10位置1,否则为0。

2.2 数据岛周期

当输入控制信号ADE(Audio Data Enable)=1时编码过程进入数据岛周期,在HDMI数据岛周期中,通过TMDS降错编码(TERC4)把三条TMDS链路上的4位音频和辅助数据编码成连续的10位直流平衡数据发送出去,这种编码是可以通过查表方式直接转换而来。

其TERC4编码方式如下:

case(D3,D2,D1,D0):

0000:q_out[9:0]=10’b10_1001_1100;

0001:q_out[9:0]=10’b10_0110_0011;

0010:q_out[9:0]=10’b10_1110_0100;

0011:q_out[9:0]=10’b10_0110_0010;

0100:q_out[9:0]=10’b01_0111_0001;

0101:q_out[9:0]=10’b01_0001_1110;

0110:q_out[9:0]=10’b01_1000_1110;

0111:q_out[9:0]=10’b01_0011_1100;

1000:q_out[9:0]=10’b10_1100_1100;

1001:q_out[9:0]=10’b01_0011_1001;

1010:q_out[9:0]=10’b01_1001_1100;

1011:q_out[9:0]=10’b10_1100_0110;

1100:q_out[9:0]=10’b10_1000_1110;

1101:q_out[9:0]=10’b10_0111_0001;

1110:q_out[9:0]=10’b01_0110_0011;

1111:q_out[9:0]=10’b10_1100_0011;

endcase

数据岛周期还存在首防护带和尾防护带,在数据岛周期中其前两个字节数据表示的是首防护带信息,后两个字节数据表示的是尾防护带信息。包括保护带在内这段时间TMDS0通道的第0位和第1位会一直对HSYNC和VSYNC两个控制信号进行编码,第2位用来指示传输的数据包头;剩下的TMDS1通道和TMDS2通道用来传输数据包。数据岛周期前向和后向防护带编码规则如下:

casa(TMDS Channel Nunmber):

0: q_out[9:0]= n.a;

1: q_out[9:0]= 0’b0100110011;

2: q_out[9:0]= 0’b0100110011;

endcase

2.3 控制周期

控制周期用于传输导言信号,同时实现发送端与接收端的字同步。当VDE或ADE有效时,TMDS链路在对实际数据进行编码之前需要输出相对应的导言和保护带信号,其中导言用来指示将要传输的数据类型。

当下一个传输周期传输视频数据时,控制信号输出视频数据导言,以视频保护带作为起始编码标志;或将要传输音频辅助数据时控制信号输出数据岛导言,以数据岛保护带作为编码起始标志。

控制周期被用于作为传输信息指南,其最主要目的是作用于两个导言(Preamble)信号的传输,采用最小差分传输编码方式在每一个TMDS时钟周期中对三个通道共6bits数据进行编码。这6bits数据包括HSYNC(行同步),VSYNC(场同步),CTL0,CTL1,CTL2 和 CTL3。其中,TMDS通道0的D0和D1分别为行同步HSYNC与场同步VSYNC;TMDS通道1的D0和D1分别为控制信号CTL0和CTL1;TMDS通道2的D0和D1分别为控制信号的CTL2和CTL3[5]。

每个控制信号在TMDS通道下的编码方式如下:

case (D1,D0):

0,0:q_out[9:0]=10’b11_0101_0100;

0,1:q_out[9:0]=10’b00_1010_1011;

1,0:q_out[9:0]=10’b01_0101_0100;

1,1:q_out[9:0]=10’b10_1010_1011;

endcase

与另外两个传输周期所得到的10位码不同,控制数据转化得到的10位码有大于或等于7个跳变,解码器可以唯一地识别这些高变换码,从而使得PLL可以利用这些确定的信号作为时钟相位校正的参考信号。

3 各工作周期信号编码仿真分析

3.1 TMDS编码模块分析

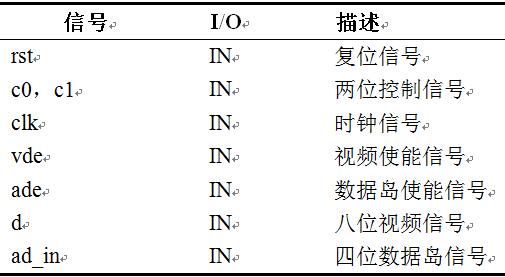

通道信号编码仿真采用的计算机硬件设备为Intel Core i5-2400 [email protected],RAM 4.00GB,仿真平台为Xilinx ISE9.1,利用Verilog语言实现TMDS的编码。源代码主要包含四个模块,它们分别为top、testbench、numbercnt、tmds四个模块。top模块用以声明TMDS编码模块中需要输入或输出的各个信号管脚;testbench模块的功能是为整个程序提供测试信号,其本身并不影响各个管脚之间的逻辑对应关系。为了全面地验证程序的逻辑和时序是否满足设计要求,需要在测试信号中前后输入各个工作周期通道信号;numbercnt模块是用以统计所输入的八位视频数据中0和1的个数,作为tmds模块中的数据转换采用异或运算还是异或非运算的判断依据;tmds模块是整个程序的核心,它定义了各个管脚的输入、输出特性以及逻辑对应关系。

3.2 激励信号编码仿真分析

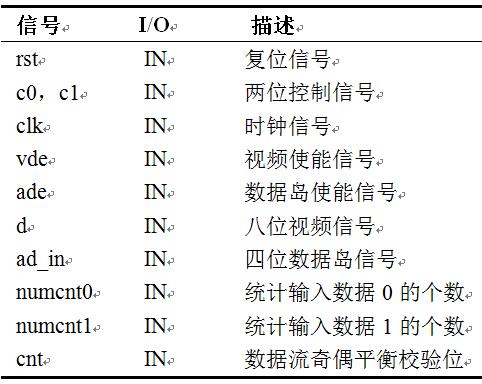

Testbench主要功能是为整个程序提供测试信号,其本身并不影响各个管脚之间的逻辑对应关系。为了全面地验证程序的逻辑和时序是否满足设计要求,需要在测试信号中前后输入各个工作周期通道信号,并在信号稳定后使其控制使能端有效,保持一段时间后才进入下一个周期的数据传输。激励信号产生模块端口说明如表2所示。

表2 单通道激励信号产生模块端口说明

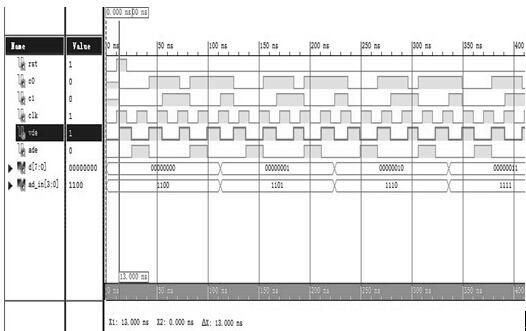

激励信号产生仿真结果如图2所示:

图2 激励信号仿真分析

在仿真开始时clk、d、ad_in、ade、vde都清零。初始化复位信号为一个正脉冲复位。利用循环结构产生由0到8'b1111_1111共256个待编码的8位视频输入信号。由图2-3传输通道具体数据格式可知,HDMI蓝色通道的D2和D3位固定为1,所以仿真激励波形中ad_in的第2和第3位的值被置为1,而第0和第1位分别从8位视频数据d的第0和第1位取得。通过程序设置对ade、vde、c0、c1值的合理设置,可以分别产生各个工作周期通道信号。

3.3 TMDS编码仿真分析

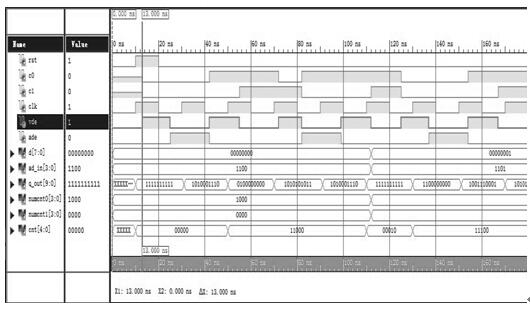

通道信号编码模块详细端口说明参见表3,其相应的单通道信号的TMDS编码仿真结果参见图3。

表3 单通道信号编码模块端口说明

通过在ModelSim6.5平台上编译源代码、仿真,得出在刺激信号作用下的输出波形如图3所示:

图3 TMDS编码仿真结果

在图3中,在rst=1时q_out处于复位状态,则编码输出值赋初值为10'b1111111111,并且用来保存数据流奇偶平衡位cnt为0;时钟信号处于上升沿且ade=1时,TMDS处于数据岛周期,q_out输出为音频数据,将输入四位音频数据1100转换为10位编码后的10_1000_1110;在时钟处于上升沿且vde=1时,TMDS处于视频数据周期,q_out输出为视频数据,将输入8位视频数据0000_0000转换为10位编码后的01_0000_0000,仿真结果输出正确;时钟处于上升沿,当ade=0和vde=0时,TMDS处于控制周期,将2位控制信号11转换为10位编码后的10_1010_1011。观察图3蓝色通道信号编码波形中各管脚的时序和逻辑电平,可以说明TMDS模块在时钟信号、复位信号和多个使能控制端的共同作用下完成了各个工作周期通道信号向10位编码的转换,满足TMDS编码要求,验证了TMDS编码的正确性。仿真结果表明TMDS编码技术能够实现数据的高效传输,确保传输数据流达到直流平衡,提高了系统的抗干扰能力。

4 结论

本文对HDMI数据通道的编码方式及过程,包括导言信号、各大工作周期保护带和编码数据的输出时序做了详细的分析,重点结合HDMI协议时序要求,深入分析控制周期、数据岛周期和视频周期数据编码方法,本文在论述TMDS编码原理的基础上完成其基于硬件描述语言verilog HDL的编程,且在Xilinx ISE9.1下验证了编码设计的正确性。仿真结果表明TMDS编码技术能够实现数据的高效传输,确保传输数据流达到直流平衡,提高了系统的抗干扰能力。

参考文献

[1] 陈文娟,林涛. HDMI标准在高清视频编码SOC设计中的应用[J].电视技术.2008(32,S1):74

[2] 张茂贵,张士刚.高清晰度多媒体接口-HDMI1.1[J].广播与电视技术.2006(3):103

[3] 刘震,陈易等.HDMI音视频接口原理[J].现代电视技术.2004,11:47

[4] 沈兰蓀,陈芳. 多媒体时代的视频技术[J]. 现代科学仪器,1995,02:20-25.

[5] http://www.hdmi.org/download/HDMI_Specification_1.1.pdf

[6] High-Definition Multimedia Interface Specification Version 1.3a Hitachi, Ltd. Matsushita Electric Industrial Co., Ltd. PhiliPs Consumer Electronics, International B.V. Silicon Image, Inc.Sony CorPoration. Thomson Inc. Toshiba CorPoration, 10, Nov, 2006.

关注本网官方微信 随时订阅权威资讯